diff --git a/.github/workflows/run-pytests.yml b/.github/workflows/run-pytests.yml

index 2da92fa39..a5bc7b237 100644

--- a/.github/workflows/run-pytests.yml

+++ b/.github/workflows/run-pytests.yml

@@ -16,4 +16,4 @@ jobs:

- run: cd proj/mnv2_first && pwd && make pytest

- run: cd proj/proj_accel_1 && pwd && make pytest

- run: cd proj/proj_template && pwd && make pytest

- - run: echo "nmigen_cfu tests"; python/nmigen_cfu/run_unit_tests.sh

+ - run: echo "amaranth_cfu tests"; python/amaranth_cfu/run_unit_tests.sh

diff --git a/.gitmodules b/.gitmodules

index f843c20b9..61e93d87b 100644

--- a/.gitmodules

+++ b/.gitmodules

@@ -25,9 +25,6 @@

[submodule "soc/deps/pythondata_cpu_vexriscv"]

path = third_party/python/pythondata_cpu_vexriscv

url = https://github.com/litex-hub/pythondata-cpu-vexriscv.git

-[submodule "third_party/python/nmigen"]

- path = third_party/python/nmigen

- url = https://github.com/nmigen/nmigen

[submodule "third_party/python/pyvcd"]

path = third_party/python/pyvcd

url = https://github.com/SanDisk-Open-Source/pyvcd.git

@@ -64,3 +61,6 @@

[submodule "third_party/python/meson"]

path = third_party/python/meson

url = https://github.com/mesonbuild/meson

+[submodule "third_party/python/amaranth"]

+ path = third_party/python/amaranth

+ url = https://github.com/amaranth-lang/amaranth

diff --git a/README.md b/README.md

index 4ee0e20f6..0cb709736 100644

--- a/README.md

+++ b/README.md

@@ -107,7 +107,7 @@ make PLATFORM=sim load

* [LiteX](https://github.com/enjoy-digital/litex): Open-source framework for assembling the SoC (CPU + peripherals)

* [VexRiscv](https://github.com/SpinalHDL/VexRiscv): Open-source RISC-V soft CPU optimized for FPGAs

-* [nMigen](https://github.com/nmigen/nmigen): Python toolbox for building digital hardware

+* [Amaranth](https://github.com/amaranth-lang/amaranth): Python toolbox for building digital hardware

### Licensed under Apache-2.0 license

diff --git a/docs/source/crash-course/gateware.rst b/docs/source/crash-course/gateware.rst

index 5105ff595..8657077b0 100644

--- a/docs/source/crash-course/gateware.rst

+++ b/docs/source/crash-course/gateware.rst

@@ -1,11 +1,11 @@

-==========================================================

-Building FPGA Gateware with Verilog and nMigen: A Tutorial

-==========================================================

+============================================================

+Building FPGA Gateware with Verilog and Amaranth: A Tutorial

+============================================================

This page takes the reader through a hands-on tutorial on FPGA, Verilog and

-nMigen_.

+Amaranth_.

-.. _nMigen: https://github.com/nmigen/nmigen

+.. _Amaranth: https://github.com/amaranth-lang/amaranth

Field Programmable Gate Arrays are fascinating devices that can efficiently

perform all kinds of computing tasks. A configuration for and FPGA is known as

@@ -16,7 +16,7 @@ well known and best supported. Learning Verilog is good way to begin to

understand how FPGAs work.

It is possible to write CFUs in Verilog, but for more sophisticated CFUs we use

-nMigen to generate Verilog.

+Amaranth to generate Verilog.

------------

Getting Help

@@ -46,7 +46,7 @@ Obtain the following:

3. Speaker with 3.5mm plug. Obtain this from eBay or any electronics store.

-4. Optional: UPduino. A small FGPA dev board which will make the nMigen

+4. Optional: UPduino. A small FGPA dev board which will make the Amaranth

tutorial a little easier and faster. (Order from tindie.)

* The UPduino often goes out of stock and sometimes delivery times are long.

* It's more than possible to run the tutorial from an Arty A7.

@@ -356,11 +356,11 @@ Counters are an important building block.

counter <= counter-1;

end

----------------------

-Part 2: nMigen Basics

----------------------

+-----------------------

+Part 2: Amaranth Basics

+-----------------------

-We're now going to dive into nMigen_, a Python based domain-specific language

+We're now going to dive into Amaranth_, a Python based domain-specific language

for writing gateware. At the lowest levels, it works much the same as

Verilog. At the higher levels, it allows all the power of Python to be applied

to generalizing, reusing and testing components.

@@ -388,7 +388,7 @@ Preparation

.. code-block:: bash

$ cd $HOME

- $ virtualenv -p python3 nmigen-tutorial

+ $ virtualenv -p python3 amaranth-tutorial

4. Add an alias to your ``.bashrc`` or ``.bash_aliases`` file:

@@ -401,19 +401,19 @@ Preparation

}

VIVADO_BIN_DIR=/home/$USER/tools/Xilinx/Vivado/2020.1/bin

FOMU_DIR=/home/$USER/fomu-toolchain-linux_x86_64-v1.5.6/bin

- alias startp='pathadd $FOMU_DIR;pathadd $VIVADO_BIN_DIR;source ~/nmigen-tutorial/bin/activate'

+ alias startp='pathadd $FOMU_DIR;pathadd $VIVADO_BIN_DIR;source ~/amaranth-tutorial/bin/activate'

5. Execute the ``startp`` alias to enter the virtual environment.

-6. Install nMigen and gtkwave used for the tutorial

+6. Install Amaranth and gtkwave used for the tutorial

.. code-block:: bash

$ sudo apt install gtkwave

$ pip install --upgrade \

- 'git+https://github.com/nmigen/nmigen.git#egg=nmigen[builtin-yosys]'

- $ pip install --upgrade 'git+https://github.com/nmigen/nmigen-boards.git'

- $ pip install --upgrade 'git+https://github.com/nmigen/nmigen-soc.git'

+ 'git+https://github.com/amaranth-lang/amaranth.git#egg=amaranth[builtin-yosys]'

+ $ pip install --upgrade 'git+https://github.com/amaranth-lang/amaranth-boards.git'

+ $ pip install --upgrade 'git+https://github.com/amaranth-lang/amaranth-soc.git'

.. hint:: You may need to install udev rules

@@ -421,9 +421,9 @@ Preparation

Vivonomicon Tutorial

====================

-Work through the `Learning FPGA Design with nMigen`_ from vivonomicon

+Work through the `Learning FPGA Design with Amaranth`_ from vivonomicon

-.. _`Learning FPGA Design with nMigen`: https://vivonomicon.com/2020/04/14/learning-fpga-design-with-nmigen/

+.. _`Learning FPGA Design with Amaranth`: https://vivonomicon.com/2020/04/14/learning-fpga-design-with-amaranth/

This is a big tutorial. Expect to spend at least half a day understanding what

is going on. This tutorial was written with the UPduino as a target, but you

@@ -432,15 +432,15 @@ code:

.. code-block:: bash

- $ cd ~/nmigen-tutorial

- $ git clone --branch updated_api https://github.com/alanvgreen/nmigen_getting_started.git

+ $ cd ~/amaranth-tutorial

+ $ git clone --branch updated_api https://github.com/alanvgreen/amaranth_getting_started.git

$ # make sure the virtualenv is activated with startp as explained above

This is a summary of the first commands in the tutorial to make sure everything is working:

.. code-block:: bash

- $ cd nmigen_getting_started/hello_nmigen

+ $ cd amaranth_getting_started/hello_amaranth

$ python3 test.py

$ gtkwave test.vcd

$ # make sure you click the zoom out icon in gtkwave after enabling the signals to view

@@ -451,14 +451,14 @@ This is a summary of the first commands in the tutorial to make sure everything

Some notes:

-* the nMigen API has changed slightly since this tutorial was written. See

+* the Amaranth API has changed slightly since this tutorial was written. See

`this PR`__ for the required updates. Because the PR has not been merged

the git clone command above will get you correct tree

-.. __: https://github.com/WRansohoff/nmigen_getting_started/pull/1

+.. __: https://github.com/WRansohoff/amaranth_getting_started/pull/1

* Do not try to cut and paste the code bits in the tutorial, they contain the outdated non

- working code. Instead use hello_nmigen/test.py from the patched tree you just cloned.

+ working code. Instead use hello_amaranth/test.py from the patched tree you just cloned.

* You may notice that the different tutorials run so quickly that it's hard to

follow the sequence of lights. can't see the sequences. Try to fix this by

@@ -466,7 +466,7 @@ Some notes:

tutorials you might want to try slowing down the main clock / oscillator like

this:

-.. _hello_led: https://github.com/WRansohoff/nmigen_getting_started/blob/master/hello_led/led.py

+.. _hello_led: https://github.com/WRansohoff/amaranth_getting_started/blob/master/hello_led/led.py

.. code:: python

@@ -533,7 +533,7 @@ If Using The Arty A7

+----------------------------------------------+------------------------------------------+

| From | To |

+==============================================+==========================================+

-| ``from nmigen_boards.upduino_v2 import *`` | ``from nmigen_boards.arty_a7 import *`` |

+| ``from amaranth_boards.upduino_v2 import *`` | ``from amaranth_boards.arty_a7 import *``|

+----------------------------------------------+------------------------------------------+

| ``grn_led = platform.request( 'led_g', 0 )`` | ``rgb = platform.request('rgb_led', 0)`` |

| ``blu_led = platform.request( 'led_b', 0 )`` | |

@@ -549,7 +549,7 @@ If Using The Arty A7

$ xc3sprog -c nexys4 build/top.bit

-* alternatively get nmigen to call xc3sprog for you by adding do_program=True to the build() call:

+* alternatively get amaranth to call xc3sprog for you by adding do_program=True to the build() call:

.. code:: bash

@@ -566,15 +566,15 @@ Recap

You now know how to:

-* Write basic nMigen code

+* Write basic Amaranth code

* Simulate a design

* Synthesize a design

* Program a real device

--------------------------------------------

-Part 3: Test Driven Development with nMigen

--------------------------------------------

+---------------------------------------------

+Part 3: Test Driven Development with Amaranth

+---------------------------------------------

That tutorial was fun, but it was missing a vital piece: unit tests. Coupled

with simulation, unit tests allow fast iteration without needing to deploy to

@@ -594,8 +594,8 @@ whenever the input transitions from low to high.

.. code:: python

- from nmigen import *

- from nmigen.sim import Simulator

+ from amaranth import *

+ from amaranth.sim import Simulator

import unittest

@@ -654,7 +654,7 @@ whenever the input transitions from low to high.

EdgeDetector and assign to a variable named "self.dut". Because it is a

submodule, we add it to our list of submodules. "DUT" means "device under

test".

- E. as we saw in the previous tutorial, nMigen uses generator functions to

+ E. as we saw in the previous tutorial, Amaranth uses generator functions to

drive the simulation. ``process()`` is a simple generator function.

F. ``run_sim()`` can optionally write a trace file. When debugging, it can

be helpful to write a tracefile.

@@ -777,8 +777,8 @@ let's create a Top() and deploy it to a real Arty board.

.. code:: python

- from nmigen import *

- from nmigen_boards.arty_a7 import *

+ from amaranth import *

+ from amaranth_boards.arty_a7 import *

from edge_detect import EdgeDetector

@@ -818,7 +818,7 @@ let's create a Top() and deploy it to a real Arty board.

that the detector only outputs '1' for a single cycle when an edge is

detected.

-.. _arty_a7.py: https://github.com/nmigen/nmigen-boards/blob/8be37da521e8789726a53bd4e0c261c12e2ab22b/nmigen_boards/arty_a7.py

+.. _arty_a7.py: https://github.com/amaranth-lang/amaranth-boards/blob/8be37da521e8789726a53bd4e0c261c12e2ab22b/amaranth_boards/arty_a7.py

3. Run it to synthesize the design and program the Arty.

4. Wait around for this to finish. Notice how long it takes and remember how

@@ -830,8 +830,8 @@ let's create a Top() and deploy it to a real Arty board.

the switch causes the LED to change.

-nMigen: Finite State Machines

-=============================

+Amaranth: Finite State Machines

+===============================

We're going to make a small example design that outputs colors in response to

button presses. In order to avoid long waits for the FPGA toolchain, we'll

@@ -1005,8 +1005,8 @@ For reference, this code worked for us:

.. code:: python

- from nmigen import *

- from nmigen_boards.arty_a7 import *

+ from amaranth import *

+ from amaranth_boards.arty_a7 import *

from edge_detect import EdgeDetector

from color_stepper import ColorStepper

@@ -1045,10 +1045,10 @@ For reference, this code worked for us:

skip.

-nMigen: Memory

-==============

+Amaranth: Memory

+================

-nMigen provides an abstraction called Memory which is useful for building

+Amaranth provides an abstraction called Memory which is useful for building

small, fast memories. The toolchain will choose exactly how it is implemented:

usually with bare flip flops if there's only a few bits or with block ram

(BRAMs) for larger memories.

@@ -1057,7 +1057,7 @@ These small, local memories are important for evaluating ML operations. Many of

them can be used in parallel, caching input data and intermediate values and so

greatly reducing the bandwidth load on main memory.

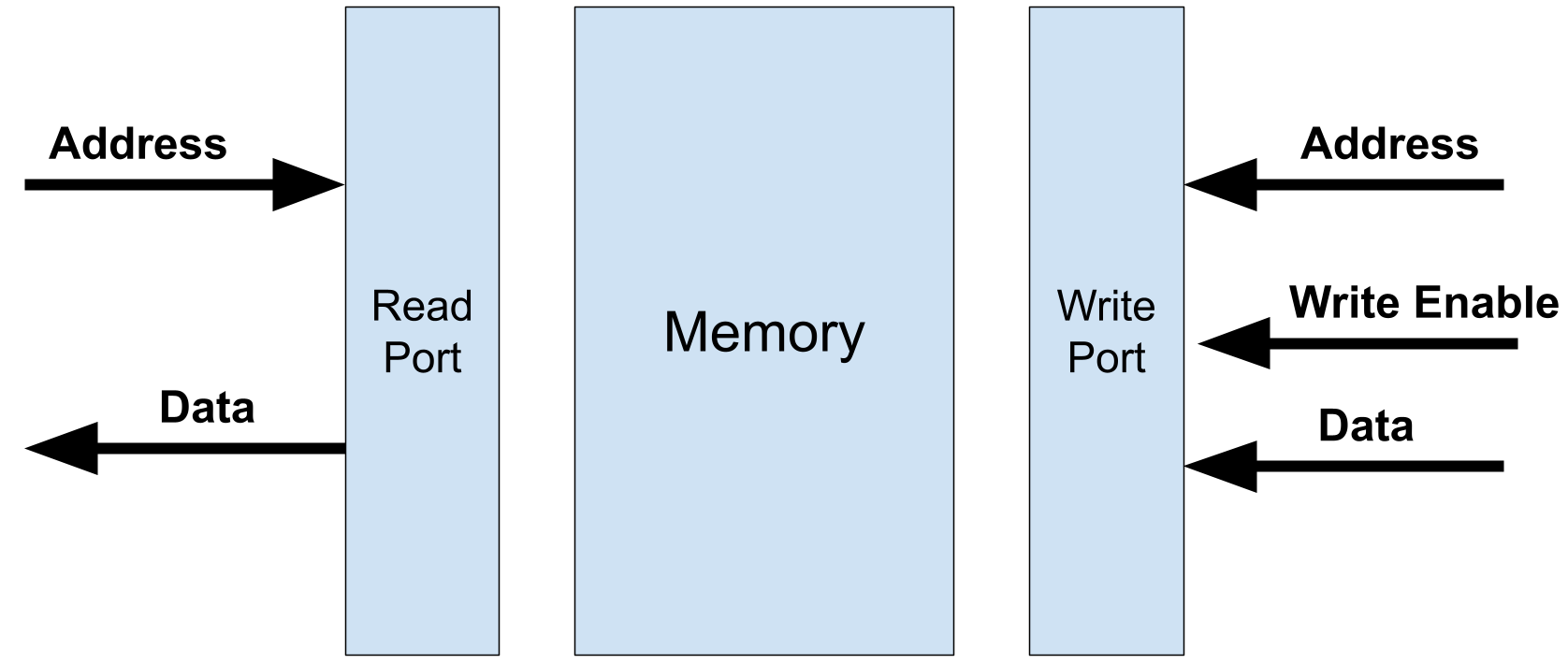

-As shown in the following diagram a typical nMigen memory has:

+As shown in the following diagram a typical Amaranth memory has:

a read port.

Every cycle, the given address lines are read and the next cycle, the data

@@ -1073,7 +1073,7 @@ even on separate clocks.

.. raw:: html

@@ -1161,7 +1161,7 @@ Further hints:

``read_addr`` signal which holds the read address - which also happens to be

the next value for addr when it is incremented.

-.. _mem.py: https://github.com/nmigen/nmigen/blob/master/nmigen/hdl/mem.py

+.. _mem.py: https://github.com/amaranth-lang/amaranth/blob/master/amaranth/hdl/mem.py

.. _`bit_length()`: https://docs.python.org/3/library/stdtypes.html#int.bit_length

And spoilers (don't read unless you're stuck):

@@ -1200,8 +1200,8 @@ lower.

Things To Do Now

----------------

-You now know enough nMigen to do quite a bit. If you'd like to experiment further, you could:

+You now know enough Amaranth to do quite a bit. If you'd like to experiment further, you could:

-* reimplement the FPGA4Fun beep tutorials in nMigen.

+* reimplement the FPGA4Fun beep tutorials in Amaranth.

* Pick up other examples from FPGA4Fun

* Move on with CFUs!

diff --git a/docs/source/crash-course/getting-help.rst b/docs/source/crash-course/getting-help.rst

index c49c9a2f9..fb8ce3edd 100644

--- a/docs/source/crash-course/getting-help.rst

+++ b/docs/source/crash-course/getting-help.rst

@@ -2,7 +2,7 @@

How To Get Help

===============

-nMigen

+Amaranth

IRC

CFU-Playground

diff --git a/docs/source/crash-course/index.rst b/docs/source/crash-course/index.rst

index 5e001db50..aadf7e07a 100644

--- a/docs/source/crash-course/index.rst

+++ b/docs/source/crash-course/index.rst

@@ -12,7 +12,7 @@ work out where the gaps in your knowledge may be.

* Tensorflow Lite for Microcontrollers

* RISCV and CFUs

-* Writing gateware with Verilog and nMigen

+* Writing gateware with Verilog and Amaranth

* LiteX and SoCs.

* Getting help.

@@ -33,7 +33,7 @@ C and C++ for Microcontrollers

a lot more code than you'll be writing.

Python

- The nMigen framework uses Python_. It is remarkably easy to learn the

+ The Amaranth framework uses Python_. It is remarkably easy to learn the

basics of Python. If you have a couple of days, we recommend working

through chapters 0 to 11 of `Dive Into Python 3`_. Dive Into Python 3 is

well paced and provides many practical exercises.

@@ -61,7 +61,7 @@ The Crash Course

:doc:`gateware`

At the lowest level, accelerators are built from gateware, and you'll need

- to know how to write Verilog and/or nMigen_.

+ to know how to write Verilog and/or Amaranth_.

:doc:`litex`

LiteX is a framework for defining FPGA SoCs. CFU-Playground accelerators

@@ -74,7 +74,7 @@ The Crash Course

:doc:`getting-help`

Building accelerators is hard. It is essential to know how to ask for help.

-.. _nMigen: https://github.com/nmigen/nmigen

+.. _Amaranth: https://github.com/amaranth-lang/amaranth

Index

diff --git a/docs/source/index.rst b/docs/source/index.rst

index 2720a92f9..0869d87c9 100644

--- a/docs/source/index.rst

+++ b/docs/source/index.rst

@@ -52,7 +52,7 @@ gateware components that make up the CFU Playground.

:doc:`setup-guide` gives detailed instructions for setting up an environment.

-:doc:`crash-course/index` explains the basics of FPGAs, Verilog, `nMigen`_,

+:doc:`crash-course/index` explains the basics of FPGAs, Verilog, `Amaranth`_,

RISCV, Custom Function Units and `Tensorflow Lite for Microcontrollers`_.

:doc:`step-by-step` will guide you through creating your first accelerator.

@@ -60,7 +60,7 @@ RISCV, Custom Function Units and `Tensorflow Lite for Microcontrollers`_.

:doc:`renode` can tell you more about simulating your project in `Renode`_.

.. _`Tensorflow Lite for Microcontrollers`: https://www.tensorflow.org/lite/microcontrollers

-.. _nMigen: https://github.com/nmigen/nmigen

+.. _Amaranth: https://github.com/amaranth-lang/amaranth

.. _Renode: https://renode.io

.. raw:: html

diff --git a/docs/source/overview.rst b/docs/source/overview.rst

index 015f130ba..7ac761dc9 100644

--- a/docs/source/overview.rst

+++ b/docs/source/overview.rst

@@ -62,14 +62,14 @@ architecture is that the CFU does not have direct access to memory. It relies

on the CPU to move data back and forth.

CFUs may be written in Verilog or with any tool that outputs Verilog. We prefer

-using nMigen_, because it has good support for composition, reuse and unit

-testing. The CFU Playground includes nMigen library components to support

+using Amaranth_, because it has good support for composition, reuse and unit

+testing. The CFU Playground includes Amaranth library components to support

CFU development.

We are currently using Vivado_ to synthesize the FPGA bitstream, and intend to move

to Symbiflow_ in the near future.

-.. _nMigen: https://github.com/nmigen/nmigen

+.. _Amaranth: https://github.com/amaranth-lang/amaranth

.. _Vivado: https://www.xilinx.com/products/design-tools/vivado.html

.. _Symbiflow: https://symbiflow.readthedocs.io/

diff --git a/docs/source/step-by-step.rst b/docs/source/step-by-step.rst

index 7c8c38f32..bfa370417 100644

--- a/docs/source/step-by-step.rst

+++ b/docs/source/step-by-step.rst

@@ -4,7 +4,7 @@ The Step-by-Step Guide to Building an ML Accelerator

After you have read the :doc:`overview ` of the CFU Playground

components and :doc:`set up ` your CFU-Playground, it's time

to accelerate a model. This tutorial will walk through the steps for building

-a basic CFU in your choice of nMigen or Verilog.

+a basic CFU in your choice of Amaranth or Verilog.

-------------------------

Step 1: Make Your Project

@@ -413,25 +413,25 @@ representation of the inputs and output of the instruction are shown below:

Now that we've described our CFU it's time to actually write the gateware. If

you'd like to implement your CFU directly in Verilog you can skip the upcoming

-section about nMigen CFUs (and likewise if you're going to be using nMigen you

+section about Amaranth CFUs (and likewise if you're going to be using Amaranth you

can skip the Verilog section).

-^^^^^^^^^^^^^^^^^^^^^^

-nMigen CFU Development

-^^^^^^^^^^^^^^^^^^^^^^

+^^^^^^^^^^^^^^^^^^^^^^^^

+Amaranth CFU Development

+^^^^^^^^^^^^^^^^^^^^^^^^

-There is a fairly robust framework for building a CFU in nMigen. Inside of

-``/python/nmigen_cfu`` there are a set of helper files

+There is a fairly robust framework for building a CFU in Amaranth. Inside of

+``/python/amaranth_cfu`` there are a set of helper files

that you can ``import`` in your code. It's best to read through the doc

-comments in ``/python/nmigen_cfu/cfu.py`` and

-``/python/nmigen_cfu/util.py`` before starting

+comments in ``/python/amaranth_cfu/cfu.py`` and

+``/python/amaranth_cfu/util.py`` before starting

development, but you should be able to get a reasonable understanding of the

framework through this example.

.. code-block:: python

- from nmigen import C, Module, Signal, signed

- from nmigen_cfu import all_words, InstructionBase, InstructionTestBase, pack_vals, simple_cfu

+ from amaranth import C, Module, Signal, signed

+ from amaranth_cfu import all_words, InstructionBase, InstructionTestBase, pack_vals, simple_cfu

import unittest

@@ -513,7 +513,7 @@ more control over the CFU. Firstly, delete the ``cfu.py`` and ``cfu_gen.py``

files from your project folder, we'll directly be creating and editing a file

named ``cfu.v``.

-When doing CFU development with nMigen, the CFU-CPU handshaking is implemented

+When doing CFU development with Amaranth, the CFU-CPU handshaking is implemented

for you in the ``Cfu`` base class. In Verilog you will need to implement your

own handshaking and for that it's important to know the CFU module

specification.

diff --git a/proj/avg_pdti8/cfu.py b/proj/avg_pdti8/cfu.py

index c239036a9..174cdcdae 100644

--- a/proj/avg_pdti8/cfu.py

+++ b/proj/avg_pdti8/cfu.py

@@ -13,8 +13,8 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Mux, Signal, signed

-from nmigen_cfu import InstructionBase, SimpleElaboratable, TestBase, Cfu, CfuTestBase

+from amaranth import Mux, Signal, signed

+from amaranth_cfu import InstructionBase, SimpleElaboratable, TestBase, Cfu, CfuTestBase

import unittest

diff --git a/proj/avg_pdti8/cfu_gen.py b/proj/avg_pdti8/cfu_gen.py

index 9864f0fee..7761d9841 100644

--- a/proj/avg_pdti8/cfu_gen.py

+++ b/proj/avg_pdti8/cfu_gen.py

@@ -13,8 +13,8 @@

# limitations under the License.

import os.path

-from nmigen import *

-from nmigen.back import rtlil, verilog

+from amaranth import *

+from amaranth.back import rtlil, verilog

from cfu import make_cfu

diff --git a/proj/avg_pdti8/util.py b/proj/avg_pdti8/util.py

index 02ad5c8d8..e9422b304 100644

--- a/proj/avg_pdti8/util.py

+++ b/proj/avg_pdti8/util.py

@@ -12,9 +12,9 @@

# WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Mux, Signal, signed

-from nmigen_cfu import SimpleElaboratable, TestBase

-from nmigen.sim import Settle

+from amaranth import Mux, Signal, signed

+from amaranth_cfu import SimpleElaboratable, TestBase

+from amaranth.sim import Settle

import unittest

diff --git a/proj/example_cfu/cfu.py b/proj/example_cfu/cfu.py

index 2117c1c7e..b0a5209b3 100755

--- a/proj/example_cfu/cfu.py

+++ b/proj/example_cfu/cfu.py

@@ -13,8 +13,8 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import *

-from nmigen_cfu import InstructionBase, InstructionTestBase, simple_cfu, CfuTestBase

+from amaranth import *

+from amaranth_cfu import InstructionBase, InstructionTestBase, simple_cfu, CfuTestBase

import unittest

diff --git a/proj/example_cfu/cfu_gen.py b/proj/example_cfu/cfu_gen.py

index 9864f0fee..7761d9841 100644

--- a/proj/example_cfu/cfu_gen.py

+++ b/proj/example_cfu/cfu_gen.py

@@ -13,8 +13,8 @@

# limitations under the License.

import os.path

-from nmigen import *

-from nmigen.back import rtlil, verilog

+from amaranth import *

+from amaranth.back import rtlil, verilog

from cfu import make_cfu

diff --git a/proj/hps_accel/cfu_gen.py b/proj/hps_accel/cfu_gen.py

index 9678df755..9cbc41bde 100644

--- a/proj/hps_accel/cfu_gen.py

+++ b/proj/hps_accel/cfu_gen.py

@@ -17,8 +17,8 @@

import os.path

import sys

-from nmigen import *

-from nmigen.back import verilog

+from amaranth import *

+from amaranth.back import verilog

from gateware.gen1.hps_cfu import make_cfu as gen1_make_cfu

from gateware.gen2.hps_cfu import make_cfu as gen2_make_cfu

diff --git a/proj/hps_accel/gateware/gen1/filter_store.py b/proj/hps_accel/gateware/gen1/filter_store.py

index 42ff17acb..f036ecfde 100644

--- a/proj/hps_accel/gateware/gen1/filter_store.py

+++ b/proj/hps_accel/gateware/gen1/filter_store.py

@@ -13,8 +13,8 @@

# limitations under the License.

-from nmigen_cfu.util import SimpleElaboratable

-from nmigen import unsigned, Signal, Module, Mux

+from amaranth_cfu.util import SimpleElaboratable

+from amaranth import unsigned, Signal, Module, Mux

from .constants import Constants

from .mem import WideReadMemory

diff --git a/proj/hps_accel/gateware/gen1/get.py b/proj/hps_accel/gateware/gen1/get.py

index f50d8d214..da4eaf7d5 100644

--- a/proj/hps_accel/gateware/gen1/get.py

+++ b/proj/hps_accel/gateware/gen1/get.py

@@ -12,10 +12,10 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import unsigned, Signal

-from nmigen.hdl.ast import Mux

-from nmigen.hdl.dsl import Module

-from nmigen_cfu import InstructionBase, SimpleElaboratable, ValueBuffer

+from amaranth import unsigned, Signal

+from amaranth.hdl.ast import Mux

+from amaranth.hdl.dsl import Module

+from amaranth_cfu import InstructionBase, SimpleElaboratable, ValueBuffer

from .constants import Constants

from ..stream import Endpoint, connect

diff --git a/proj/hps_accel/gateware/gen1/hps_cfu.py b/proj/hps_accel/gateware/gen1/hps_cfu.py

index 32f28eff3..60c612eb2 100644

--- a/proj/hps_accel/gateware/gen1/hps_cfu.py

+++ b/proj/hps_accel/gateware/gen1/hps_cfu.py

@@ -12,9 +12,9 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Signal, signed, unsigned

-from nmigen.hdl.rec import Layout

-from nmigen_cfu import Cfu, InstructionBase, SimpleElaboratable, all_words

+from amaranth import Signal, signed, unsigned

+from amaranth.hdl.rec import Layout

+from amaranth_cfu import Cfu, InstructionBase, SimpleElaboratable, all_words

from .constants import Constants

from .filter_store import FilterStore

diff --git a/proj/hps_accel/gateware/gen1/input_store.py b/proj/hps_accel/gateware/gen1/input_store.py

index 3c0c5e37b..e191450a1 100644

--- a/proj/hps_accel/gateware/gen1/input_store.py

+++ b/proj/hps_accel/gateware/gen1/input_store.py

@@ -13,8 +13,8 @@

# limitations under the License.

-from nmigen_cfu.util import SimpleElaboratable

-from nmigen import unsigned, Signal, Module, Mux

+from amaranth_cfu.util import SimpleElaboratable

+from amaranth import unsigned, Signal, Module, Mux

from .constants import Constants

from .mem import WideReadMemory

diff --git a/proj/hps_accel/gateware/gen1/macc.py b/proj/hps_accel/gateware/gen1/macc.py

index 0fa13a82c..5441dd44d 100644

--- a/proj/hps_accel/gateware/gen1/macc.py

+++ b/proj/hps_accel/gateware/gen1/macc.py

@@ -14,9 +14,9 @@

# limitations under the License.

-from nmigen import Array, Shape, Signal, signed

-from nmigen.hdl.rec import Layout

-from nmigen_cfu.util import all_words, tree_sum, SimpleElaboratable

+from amaranth import Array, Shape, Signal, signed

+from amaranth.hdl.rec import Layout

+from amaranth_cfu.util import all_words, tree_sum, SimpleElaboratable

from ..stream import Endpoint

diff --git a/proj/hps_accel/gateware/gen1/mem.py b/proj/hps_accel/gateware/gen1/mem.py

index 0d0188190..af739ff94 100644

--- a/proj/hps_accel/gateware/gen1/mem.py

+++ b/proj/hps_accel/gateware/gen1/mem.py

@@ -12,8 +12,8 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Cat, Memory, Module, Signal

-from nmigen_cfu.util import SimpleElaboratable

+from amaranth import Cat, Memory, Module, Signal

+from amaranth_cfu.util import SimpleElaboratable

class WideReadMemory(SimpleElaboratable):

diff --git a/proj/hps_accel/gateware/gen1/post_process.py b/proj/hps_accel/gateware/gen1/post_process.py

index ff8b8d128..b9688a645 100644

--- a/proj/hps_accel/gateware/gen1/post_process.py

+++ b/proj/hps_accel/gateware/gen1/post_process.py

@@ -13,8 +13,8 @@

# limitations under the License.

-from nmigen_cfu import SimpleElaboratable, InstructionBase

-from nmigen import signed, unsigned, Memory, Module, Mux, Record, Signal

+from amaranth_cfu import SimpleElaboratable, InstructionBase

+from amaranth import signed, unsigned, Memory, Module, Mux, Record, Signal

from ..stream import BinaryPipelineActor

from ..stream.gearbox import ByteToWord

diff --git a/proj/hps_accel/gateware/gen1/set.py b/proj/hps_accel/gateware/gen1/set.py

index 2c8d6f112..c53b91821 100644

--- a/proj/hps_accel/gateware/gen1/set.py

+++ b/proj/hps_accel/gateware/gen1/set.py

@@ -12,9 +12,9 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Signal, unsigned

-from nmigen.hdl.dsl import Module

-from nmigen_cfu import InstructionBase, SimpleElaboratable

+from amaranth import Signal, unsigned

+from amaranth.hdl.dsl import Module

+from amaranth_cfu import InstructionBase, SimpleElaboratable

from .constants import Constants

from ..stream import Endpoint, connect

diff --git a/proj/hps_accel/gateware/gen1/sp_mem.py b/proj/hps_accel/gateware/gen1/sp_mem.py

index 930f3123a..6df173b48 100644

--- a/proj/hps_accel/gateware/gen1/sp_mem.py

+++ b/proj/hps_accel/gateware/gen1/sp_mem.py

@@ -13,12 +13,12 @@

# limitations under the License.

from migen.fhdl.structure import Mux

-from nmigen import unsigned

-from nmigen.hdl.ast import Shape, Signal

-from nmigen.hdl.dsl import Module

-from nmigen.hdl.mem import Memory

-from nmigen.hdl.rec import DIR_FANOUT, Layout

-from nmigen_cfu.util import SimpleElaboratable, ValueBuffer

+from amaranth import unsigned

+from amaranth.hdl.ast import Shape, Signal

+from amaranth.hdl.dsl import Module

+from amaranth.hdl.mem import Memory

+from amaranth.hdl.rec import DIR_FANOUT, Layout

+from amaranth_cfu.util import SimpleElaboratable, ValueBuffer

from ..stream import Endpoint, Buffer, connect

@@ -42,11 +42,11 @@ def __init__(self, *, width, depth):

self.depth = depth

def addr_shape(self) -> Shape:

- """nMigen shape describing the address."""

+ """Amaranth shape describing the address."""

return unsigned((self.depth - 1).bit_length())

def data_shape(self) -> Shape:

- """nMigen shape describing a data word."""

+ """Amaranth shape describing a data word."""

return unsigned(self.width)

def write_stream_payload_type(self) -> Layout:

diff --git a/proj/hps_accel/gateware/gen1/test_filter_store.py b/proj/hps_accel/gateware/gen1/test_filter_store.py

index d80fefd33..392db95c7 100644

--- a/proj/hps_accel/gateware/gen1/test_filter_store.py

+++ b/proj/hps_accel/gateware/gen1/test_filter_store.py

@@ -13,9 +13,9 @@

# limitations under the License.

-from nmigen.sim.core import Settle

-from nmigen_cfu import TestBase

-from nmigen_cfu.util import pack128

+from amaranth.sim.core import Settle

+from amaranth_cfu import TestBase

+from amaranth_cfu.util import pack128

from .filter_store import FilterStore

diff --git a/proj/hps_accel/gateware/gen1/test_get.py b/proj/hps_accel/gateware/gen1/test_get.py

index 1ca773c45..fdcf366cf 100644

--- a/proj/hps_accel/gateware/gen1/test_get.py

+++ b/proj/hps_accel/gateware/gen1/test_get.py

@@ -14,8 +14,8 @@

# limitations under the License.

-from nmigen.sim import Delay

-from nmigen_cfu import TestBase

+from amaranth.sim import Delay

+from amaranth_cfu import TestBase

from .constants import Constants

from .get import StatusRegister, GetInstruction

diff --git a/proj/hps_accel/gateware/gen1/test_hps_cfu.py b/proj/hps_accel/gateware/gen1/test_hps_cfu.py

index d396c89ab..dc25a5147 100644

--- a/proj/hps_accel/gateware/gen1/test_hps_cfu.py

+++ b/proj/hps_accel/gateware/gen1/test_hps_cfu.py

@@ -14,9 +14,9 @@

from random import seed, randint

-from nmigen.sim import Settle

-from nmigen_cfu import CfuTestBase, InstructionTestBase, pack_vals

-from nmigen_cfu.util import TestBase

+from amaranth.sim import Settle

+from amaranth_cfu import CfuTestBase, InstructionTestBase, pack_vals

+from amaranth_cfu.util import TestBase

from .constants import Constants

from .hps_cfu import PingInstruction, ResultAccumulator, make_cfu

diff --git a/proj/hps_accel/gateware/gen1/test_input_store.py b/proj/hps_accel/gateware/gen1/test_input_store.py

index bbd3ee6c9..3c38092cf 100644

--- a/proj/hps_accel/gateware/gen1/test_input_store.py

+++ b/proj/hps_accel/gateware/gen1/test_input_store.py

@@ -14,9 +14,9 @@

# limitations under the License.

-from nmigen.sim import Delay

-from nmigen_cfu import TestBase

-from nmigen_cfu.util import pack128

+from amaranth.sim import Delay

+from amaranth_cfu import TestBase

+from amaranth_cfu.util import pack128

from .input_store import Signal, InputStore

diff --git a/proj/hps_accel/gateware/gen1/test_macc.py b/proj/hps_accel/gateware/gen1/test_macc.py

index 4fe94212a..2176e5fda 100644

--- a/proj/hps_accel/gateware/gen1/test_macc.py

+++ b/proj/hps_accel/gateware/gen1/test_macc.py

@@ -14,10 +14,10 @@

# limitations under the License.

-from nmigen.hdl.ast import Cat, Const, signed

-from nmigen.sim import Settle, Tick

+from amaranth.hdl.ast import Cat, Const, signed

+from amaranth.sim import Settle, Tick

-from nmigen_cfu import TestBase

+from amaranth_cfu import TestBase

from .macc import MultiplyAccumulate

diff --git a/proj/hps_accel/gateware/gen1/test_mem.py b/proj/hps_accel/gateware/gen1/test_mem.py

index f48c2709d..a473e0ed9 100644

--- a/proj/hps_accel/gateware/gen1/test_mem.py

+++ b/proj/hps_accel/gateware/gen1/test_mem.py

@@ -14,8 +14,8 @@

# limitations under the License.

-from nmigen.sim import Delay

-from nmigen_cfu import TestBase

+from amaranth.sim import Delay

+from amaranth_cfu import TestBase

from .mem import WideReadMemory

diff --git a/proj/hps_accel/gateware/gen1/test_post_process.py b/proj/hps_accel/gateware/gen1/test_post_process.py

index b4e7df8ed..fb2aff257 100644

--- a/proj/hps_accel/gateware/gen1/test_post_process.py

+++ b/proj/hps_accel/gateware/gen1/test_post_process.py

@@ -15,8 +15,8 @@

import random

-from nmigen.sim import Delay

-from nmigen_cfu import TestBase

+from amaranth.sim import Delay

+from amaranth_cfu import TestBase

from .post_process import (SaturatingRoundingDoubleHighMul, RoundingDivideByPowerOfTwo,

OutputParamsStorage, SaturateActivationPipeline,

diff --git a/proj/hps_accel/gateware/gen1/test_set.py b/proj/hps_accel/gateware/gen1/test_set.py

index becbd3018..817baba23 100644

--- a/proj/hps_accel/gateware/gen1/test_set.py

+++ b/proj/hps_accel/gateware/gen1/test_set.py

@@ -14,8 +14,8 @@

# limitations under the License.

-from nmigen.sim import Delay

-from nmigen_cfu import TestBase

+from amaranth.sim import Delay

+from amaranth_cfu import TestBase

from .constants import Constants

from .set import ConfigurationRegister, SetInstruction

diff --git a/proj/hps_accel/gateware/gen1/test_sp_mem.py b/proj/hps_accel/gateware/gen1/test_sp_mem.py

index b051b503b..438bd340a 100644

--- a/proj/hps_accel/gateware/gen1/test_sp_mem.py

+++ b/proj/hps_accel/gateware/gen1/test_sp_mem.py

@@ -14,8 +14,8 @@

# limitations under the License.

-from nmigen.sim import Settle

-from nmigen_cfu import TestBase

+from amaranth.sim import Settle

+from amaranth_cfu import TestBase

from .sp_mem import MemoryParameters, SinglePortMemory

diff --git a/proj/hps_accel/gateware/gen2/accelerator.py b/proj/hps_accel/gateware/gen2/accelerator.py

index dbd262fb8..7f70d1c46 100644

--- a/proj/hps_accel/gateware/gen2/accelerator.py

+++ b/proj/hps_accel/gateware/gen2/accelerator.py

@@ -15,7 +15,7 @@

"""Accelerator Gateware"""

-from nmigen import (

+from amaranth import (

Const,

Memory,

Mux,

@@ -24,7 +24,7 @@

Signal,

signed,

unsigned)

-from nmigen_cfu.util import SimpleElaboratable

+from amaranth_cfu.util import SimpleElaboratable

from ..stream import connect, Endpoint

from .constants import Constants

diff --git a/proj/hps_accel/gateware/gen2/filter.py b/proj/hps_accel/gateware/gen2/filter.py

index d2f05b41c..c8a6ef266 100644

--- a/proj/hps_accel/gateware/gen2/filter.py

+++ b/proj/hps_accel/gateware/gen2/filter.py

@@ -15,8 +15,8 @@

"""Gateware for filter storage."""

-from nmigen import Mux, Signal, unsigned

-from nmigen_cfu import SequentialMemoryReader, SimpleElaboratable

+from amaranth import Mux, Signal, unsigned

+from amaranth_cfu import SequentialMemoryReader, SimpleElaboratable

from ..stream import Endpoint

from .constants import Constants

diff --git a/proj/hps_accel/gateware/gen2/hps_cfu.py b/proj/hps_accel/gateware/gen2/hps_cfu.py

index c4d07dbba..f65e588eb 100644

--- a/proj/hps_accel/gateware/gen2/hps_cfu.py

+++ b/proj/hps_accel/gateware/gen2/hps_cfu.py

@@ -12,8 +12,8 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Cat, Mux, Record, Signal, signed, unsigned

-from nmigen_cfu import Cfu, InstructionBase

+from amaranth import Cat, Mux, Record, Signal, signed, unsigned

+from amaranth_cfu import Cfu, InstructionBase

from .accelerator import AcceleratorCore, ACCELERATOR_CONFIGURATION_LAYOUT

from .constants import Constants

diff --git a/proj/hps_accel/gateware/gen2/macc.py b/proj/hps_accel/gateware/gen2/macc.py

index 64535c664..034e4f846 100644

--- a/proj/hps_accel/gateware/gen2/macc.py

+++ b/proj/hps_accel/gateware/gen2/macc.py

@@ -16,8 +16,8 @@

"""Multiply Accumulate Blocks for a systolic array"""

-from nmigen import Mux, Signal, unsigned, Const, Instance, ClockSignal, ResetSignal, Cat

-from nmigen_cfu.util import tree_sum, SimpleElaboratable

+from amaranth import Mux, Signal, unsigned, Const, Instance, ClockSignal, ResetSignal, Cat

+from amaranth_cfu.util import tree_sum, SimpleElaboratable

from .utils import delay

diff --git a/proj/hps_accel/gateware/gen2/mem.py b/proj/hps_accel/gateware/gen2/mem.py

index 602815982..c653b92c0 100644

--- a/proj/hps_accel/gateware/gen2/mem.py

+++ b/proj/hps_accel/gateware/gen2/mem.py

@@ -15,8 +15,8 @@

"""Simple memory wrapper"""

-from nmigen import Memory, Mux, Signal, unsigned

-from nmigen_cfu.util import SimpleElaboratable

+from amaranth import Memory, Mux, Signal, unsigned

+from amaranth_cfu.util import SimpleElaboratable

from ..stream import Endpoint

from .utils import unsigned_upto

@@ -29,7 +29,7 @@ class SinglePortMemory(SimpleElaboratable):

write occurs at the same time as a read, the write takes precedence,

and the output data is invalid.

- This is a simple wrapper for the nmigen library Memory, and in future

+ This is a simple wrapper for the amaranth library Memory, and in future

may be replaced with an implementation based on FPGA-specific

primitives.

diff --git a/proj/hps_accel/gateware/gen2/mode0_input.py b/proj/hps_accel/gateware/gen2/mode0_input.py

index 0e48d60b6..bfe0739bb 100644

--- a/proj/hps_accel/gateware/gen2/mode0_input.py

+++ b/proj/hps_accel/gateware/gen2/mode0_input.py

@@ -26,8 +26,8 @@

Data is read through the RamMux, allowing two words to be read on every cycle.

"""

-from nmigen import Cat, Mux, Signal

-from nmigen_cfu.util import SimpleElaboratable

+from amaranth import Cat, Mux, Signal

+from amaranth_cfu.util import SimpleElaboratable

from .ram_mux import RamMux

from .utils import unsigned_upto

diff --git a/proj/hps_accel/gateware/gen2/mode1_input.py b/proj/hps_accel/gateware/gen2/mode1_input.py

index f92481753..073a1a496 100644

--- a/proj/hps_accel/gateware/gen2/mode1_input.py

+++ b/proj/hps_accel/gateware/gen2/mode1_input.py

@@ -68,8 +68,8 @@

addresses for all the data for a given output pixel from that start address.

"""

-from nmigen import Array, Mux, Signal, unsigned

-from nmigen_cfu.util import SimpleElaboratable

+from amaranth import Array, Mux, Signal, unsigned

+from amaranth_cfu.util import SimpleElaboratable

from .utils import unsigned_upto

diff --git a/proj/hps_accel/gateware/gen2/post_process.py b/proj/hps_accel/gateware/gen2/post_process.py

index e85f31a50..0405ea315 100644

--- a/proj/hps_accel/gateware/gen2/post_process.py

+++ b/proj/hps_accel/gateware/gen2/post_process.py

@@ -14,8 +14,8 @@

"""Post processing of accumulated values into 8 bit outputs."""

-from nmigen_cfu import SimpleElaboratable

-from nmigen import (

+from amaranth_cfu import SimpleElaboratable

+from amaranth import (

signed, unsigned, Array, Cat, Module, Mux, Record, Signal, ResetInserter

)

diff --git a/proj/hps_accel/gateware/gen2/ram_mux.py b/proj/hps_accel/gateware/gen2/ram_mux.py

index bafdb3e44..51e9744d1 100644

--- a/proj/hps_accel/gateware/gen2/ram_mux.py

+++ b/proj/hps_accel/gateware/gen2/ram_mux.py

@@ -12,8 +12,8 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Signal

-from nmigen_cfu.util import SimpleElaboratable

+from amaranth import Signal

+from amaranth_cfu.util import SimpleElaboratable

class RamMux(SimpleElaboratable):

diff --git a/proj/hps_accel/gateware/gen2/sysarray.py b/proj/hps_accel/gateware/gen2/sysarray.py

index 0ffe6d737..a0303d751 100644

--- a/proj/hps_accel/gateware/gen2/sysarray.py

+++ b/proj/hps_accel/gateware/gen2/sysarray.py

@@ -14,8 +14,8 @@

"""Gateware for the accelerator."""

-from nmigen import Signal, signed, unsigned

-from nmigen_cfu import SimpleElaboratable

+from amaranth import Signal, signed, unsigned

+from amaranth_cfu import SimpleElaboratable

from .constants import Constants

from .macc import get_macc_block_class

diff --git a/proj/hps_accel/gateware/gen2/test_accelerator.py b/proj/hps_accel/gateware/gen2/test_accelerator.py

index 03b9ff987..a7558ebbb 100644

--- a/proj/hps_accel/gateware/gen2/test_accelerator.py

+++ b/proj/hps_accel/gateware/gen2/test_accelerator.py

@@ -18,10 +18,10 @@

from functools import reduce

import random

-from nmigen import Module, signed, unsigned

-from nmigen.sim import Passive

+from amaranth import Module, signed, unsigned

+from amaranth.sim import Passive

-from nmigen_cfu import pack_vals, TestBase

+from amaranth_cfu import pack_vals, TestBase

from .accelerator import AcceleratorCore

from .constants import Constants

diff --git a/proj/hps_accel/gateware/gen2/test_filter.py b/proj/hps_accel/gateware/gen2/test_filter.py

index 296cc0dc1..3a00e2054 100644

--- a/proj/hps_accel/gateware/gen2/test_filter.py

+++ b/proj/hps_accel/gateware/gen2/test_filter.py

@@ -15,7 +15,7 @@

"""Tests for filter.py"""

-from nmigen_cfu import TestBase

+from amaranth_cfu import TestBase

from .filter import FilterStore

diff --git a/proj/hps_accel/gateware/gen2/test_hps_cfu.py b/proj/hps_accel/gateware/gen2/test_hps_cfu.py

index 3acee4f9a..e39d6d5f5 100644

--- a/proj/hps_accel/gateware/gen2/test_hps_cfu.py

+++ b/proj/hps_accel/gateware/gen2/test_hps_cfu.py

@@ -15,8 +15,8 @@

"""Tests for hps_cfu.py"""

-from nmigen_cfu import CfuTestBase, InstructionTestBase, pack_vals

-from nmigen.sim import Passive

+from amaranth_cfu import CfuTestBase, InstructionTestBase, pack_vals

+from amaranth.sim import Passive

from .constants import Constants

from .conv2d_data import fetch_data

diff --git a/proj/hps_accel/gateware/gen2/test_macc.py b/proj/hps_accel/gateware/gen2/test_macc.py

index e920a14fa..644e8a9d9 100644

--- a/proj/hps_accel/gateware/gen2/test_macc.py

+++ b/proj/hps_accel/gateware/gen2/test_macc.py

@@ -18,10 +18,10 @@

from collections import namedtuple

import random

-from nmigen import unsigned, signed

-from nmigen.sim import Delay

+from amaranth import unsigned, signed

+from amaranth.sim import Delay

-from nmigen_cfu import TestBase

+from amaranth_cfu import TestBase

from .macc import StandardMaccBlock

diff --git a/proj/hps_accel/gateware/gen2/test_mem.py b/proj/hps_accel/gateware/gen2/test_mem.py

index c02886edf..20f7a0d5b 100644

--- a/proj/hps_accel/gateware/gen2/test_mem.py

+++ b/proj/hps_accel/gateware/gen2/test_mem.py

@@ -17,8 +17,8 @@

import random

-from nmigen.sim import Delay

-from nmigen_cfu import TestBase

+from amaranth.sim import Delay

+from amaranth_cfu import TestBase

from .mem import LoopingAddressGenerator, LoopingCounter, SinglePortMemory

diff --git a/proj/hps_accel/gateware/gen2/test_mode0_input.py b/proj/hps_accel/gateware/gen2/test_mode0_input.py

index c7b237be1..44a9dc22c 100644

--- a/proj/hps_accel/gateware/gen2/test_mode0_input.py

+++ b/proj/hps_accel/gateware/gen2/test_mode0_input.py

@@ -14,9 +14,9 @@

"""Tests for mode0_input.py"""

-from nmigen import Memory

-from nmigen_cfu import TestBase

-from nmigen_cfu.util import pack_vals

+from amaranth import Memory

+from amaranth_cfu import TestBase

+from amaranth_cfu.util import pack_vals

from .conv2d_data import fetch_data

from .mode0_input import (

diff --git a/proj/hps_accel/gateware/gen2/test_mode1_input.py b/proj/hps_accel/gateware/gen2/test_mode1_input.py

index 42e1dca10..fc7f95af2 100644

--- a/proj/hps_accel/gateware/gen2/test_mode1_input.py

+++ b/proj/hps_accel/gateware/gen2/test_mode1_input.py

@@ -16,9 +16,9 @@

import itertools

-from nmigen import Memory, unsigned

-from nmigen.sim import Passive, Delay, Settle

-from nmigen_cfu import TestBase

+from amaranth import Memory, unsigned

+from amaranth.sim import Passive, Delay, Settle

+from amaranth_cfu import TestBase

from .conv2d_data import fetch_data

from .mode1_input import (

diff --git a/proj/hps_accel/gateware/gen2/test_post_process.py b/proj/hps_accel/gateware/gen2/test_post_process.py

index 5381963a8..6fcb7fe0c 100644

--- a/proj/hps_accel/gateware/gen2/test_post_process.py

+++ b/proj/hps_accel/gateware/gen2/test_post_process.py

@@ -17,10 +17,10 @@

import itertools

import random

-from nmigen import Module, unsigned

-from nmigen.sim import Passive, Delay

+from amaranth import Module, unsigned

+from amaranth.sim import Passive, Delay

-from nmigen_cfu import pack_vals, TestBase

+from amaranth_cfu import pack_vals, TestBase

from .post_process import (

SaturatingRoundingDoubleHighMul, RoundingDivideByPowerOfTwo,

diff --git a/proj/hps_accel/gateware/gen2/test_ram_mux.py b/proj/hps_accel/gateware/gen2/test_ram_mux.py

index 6c1b29f02..a8311d4e5 100644

--- a/proj/hps_accel/gateware/gen2/test_ram_mux.py

+++ b/proj/hps_accel/gateware/gen2/test_ram_mux.py

@@ -16,9 +16,9 @@

import itertools

-from nmigen import unsigned

-from nmigen.sim import Passive

-from nmigen_cfu import TestBase

+from amaranth import unsigned

+from amaranth.sim import Passive

+from amaranth_cfu import TestBase

from .conv2d_data import fetch_data

from .ram_mux import RamMux

diff --git a/proj/hps_accel/gateware/gen2/test_sysarray.py b/proj/hps_accel/gateware/gen2/test_sysarray.py

index 5f1b85e41..eee1d35d7 100644

--- a/proj/hps_accel/gateware/gen2/test_sysarray.py

+++ b/proj/hps_accel/gateware/gen2/test_sysarray.py

@@ -17,10 +17,10 @@

import random

-from nmigen import Cat, Const, Module, signed

-from nmigen.sim import Passive, Delay

+from amaranth import Cat, Const, Module, signed

+from amaranth.sim import Passive, Delay

-from nmigen_cfu import TestBase

+from amaranth_cfu import TestBase

from .sysarray import SystolicArray

diff --git a/proj/hps_accel/gateware/gen2/test_utils.py b/proj/hps_accel/gateware/gen2/test_utils.py

index 9ef6cf295..8720d5a07 100644

--- a/proj/hps_accel/gateware/gen2/test_utils.py

+++ b/proj/hps_accel/gateware/gen2/test_utils.py

@@ -15,8 +15,8 @@

"""Tests for uitls.py"""

-from nmigen import Signal, Module

-from nmigen_cfu import TestBase

+from amaranth import Signal, Module

+from amaranth_cfu import TestBase

from .utils import delay

import random

diff --git a/proj/hps_accel/gateware/gen2/utils.py b/proj/hps_accel/gateware/gen2/utils.py

index fbf1cf8ee..b6a2a771d 100644

--- a/proj/hps_accel/gateware/gen2/utils.py

+++ b/proj/hps_accel/gateware/gen2/utils.py

@@ -14,7 +14,7 @@

"""Utility functions."""

-from nmigen import Signal, unsigned

+from amaranth import Signal, unsigned

def unsigned_upto(maximum_value):

diff --git a/proj/hps_accel/gateware/stream/__init__.py b/proj/hps_accel/gateware/stream/__init__.py

index 578f31e62..b52238520 100644

--- a/proj/hps_accel/gateware/stream/__init__.py

+++ b/proj/hps_accel/gateware/stream/__init__.py

@@ -50,9 +50,9 @@

wait for a handshake, it declares this in its Definition.

This implementation was heavily influenced by the discussion at

-https://github.com/nmigen/nmigen/issues/317, and especially the existing design

-of LiteX streams. It relies heavily on the nmigen Record class for payload

-manipulation.

+https://github.com/amaranth-lang/amaranth/issues/317, and especially the

+existing design of LiteX streams. It relies heavily on the amaranth Record class

+for payload manipulation.

Major differences from LiteX Streams:

diff --git a/proj/hps_accel/gateware/stream/actor.py b/proj/hps_accel/gateware/stream/actor.py

index a748db947..f1fa8a7b9 100644

--- a/proj/hps_accel/gateware/stream/actor.py

+++ b/proj/hps_accel/gateware/stream/actor.py

@@ -13,8 +13,8 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Cat, Signal, Module

-from nmigen_cfu import SimpleElaboratable

+from amaranth import Cat, Signal, Module

+from amaranth_cfu import SimpleElaboratable

from .stream import PayloadDefinition, Endpoint

diff --git a/proj/hps_accel/gateware/stream/buffer.py b/proj/hps_accel/gateware/stream/buffer.py

index 9f208fdd1..bac564ea7 100644

--- a/proj/hps_accel/gateware/stream/buffer.py

+++ b/proj/hps_accel/gateware/stream/buffer.py

@@ -12,10 +12,10 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen_cfu.util import SimpleElaboratable

-from nmigen import Value, Module, Signal, Mux

-from nmigen.hdl.ast import Cat

-from nmigen.hdl.rec import Layout

+from amaranth_cfu.util import SimpleElaboratable

+from amaranth import Value, Module, Signal, Mux

+from amaranth.hdl.ast import Cat

+from amaranth.hdl.rec import Layout

from .stream import Endpoint

diff --git a/proj/hps_accel/gateware/stream/fifo.py b/proj/hps_accel/gateware/stream/fifo.py

index 00e559739..3df1bf12f 100644

--- a/proj/hps_accel/gateware/stream/fifo.py

+++ b/proj/hps_accel/gateware/stream/fifo.py

@@ -14,10 +14,10 @@

# limitations under the License.

-from nmigen import signed, unsigned, Cat, Signal, Module

-from nmigen.lib.fifo import SyncFIFOBuffered

-from nmigen.hdl.dsl import FSM

-from nmigen_cfu import SimpleElaboratable

+from amaranth import signed, unsigned, Cat, Signal, Module

+from amaranth.lib.fifo import SyncFIFOBuffered

+from amaranth.hdl.dsl import FSM

+from amaranth_cfu import SimpleElaboratable

from .stream import PayloadDefinition, Endpoint

diff --git a/proj/hps_accel/gateware/stream/flow.py b/proj/hps_accel/gateware/stream/flow.py

index 1c673de31..51f338a3a 100644

--- a/proj/hps_accel/gateware/stream/flow.py

+++ b/proj/hps_accel/gateware/stream/flow.py

@@ -12,7 +12,7 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Signal, unsigned

+from amaranth import Signal, unsigned

from .actor import BinaryActor

from .stream import Endpoint

diff --git a/proj/hps_accel/gateware/stream/gearbox.py b/proj/hps_accel/gateware/stream/gearbox.py

index d67c2ba03..73f0b85e2 100644

--- a/proj/hps_accel/gateware/stream/gearbox.py

+++ b/proj/hps_accel/gateware/stream/gearbox.py

@@ -14,9 +14,9 @@

# limitations under the License.

-from nmigen import signed, unsigned, Cat, Signal, Module

-from nmigen.hdl.dsl import FSM

-from nmigen_cfu import SimpleElaboratable

+from amaranth import signed, unsigned, Cat, Signal, Module

+from amaranth.hdl.dsl import FSM

+from amaranth_cfu import SimpleElaboratable

from .stream import Endpoint

diff --git a/proj/hps_accel/gateware/stream/stream.py b/proj/hps_accel/gateware/stream/stream.py

index f728f6d0f..25137752f 100644

--- a/proj/hps_accel/gateware/stream/stream.py

+++ b/proj/hps_accel/gateware/stream/stream.py

@@ -13,8 +13,8 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Shape

-from nmigen.hdl.rec import Layout, Record

+from amaranth import Shape

+from amaranth.hdl.rec import Layout, Record

__all__ = ['PayloadDefinition', 'Endpoint', 'connect']

diff --git a/proj/hps_accel/gateware/stream/test_buffer.py b/proj/hps_accel/gateware/stream/test_buffer.py

index d85f7c8a1..9266b2df0 100644

--- a/proj/hps_accel/gateware/stream/test_buffer.py

+++ b/proj/hps_accel/gateware/stream/test_buffer.py

@@ -13,12 +13,12 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import unsigned

-from nmigen.hdl.rec import Layout

-from nmigen.sim.core import Delay, Settle

+from amaranth import unsigned

+from amaranth.hdl.rec import Layout

+from amaranth.sim.core import Delay, Settle

-from nmigen_cfu.util import TestBase

+from amaranth_cfu.util import TestBase

from .buffer import Buffer, ConcatenatingBuffer

diff --git a/proj/hps_accel/gateware/stream/test_flow.py b/proj/hps_accel/gateware/stream/test_flow.py

index 1a1ad2c44..12f52457e 100644

--- a/proj/hps_accel/gateware/stream/test_flow.py

+++ b/proj/hps_accel/gateware/stream/test_flow.py

@@ -12,11 +12,11 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import unsigned

-from nmigen.hdl.rec import Layout

-from nmigen.sim.core import Settle

+from amaranth import unsigned

+from amaranth.hdl.rec import Layout

+from amaranth.sim.core import Settle

-from nmigen_cfu.util import TestBase

+from amaranth_cfu.util import TestBase

from .flow import FlowRestrictor

diff --git a/proj/hps_accel/gateware/stream/test_gearbox.py b/proj/hps_accel/gateware/stream/test_gearbox.py

index b22c01dc3..1018304b8 100644

--- a/proj/hps_accel/gateware/stream/test_gearbox.py

+++ b/proj/hps_accel/gateware/stream/test_gearbox.py

@@ -13,11 +13,11 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import unsigned

-from nmigen.sim.core import Delay

+from amaranth import unsigned

+from amaranth.sim.core import Delay

-from nmigen_cfu.util import TestBase

+from amaranth_cfu.util import TestBase

from .gearbox import ByteToWord

diff --git a/proj/hps_accel/gateware/stream/test_stream.py b/proj/hps_accel/gateware/stream/test_stream.py

index ceafe0eb5..44aff4593 100644

--- a/proj/hps_accel/gateware/stream/test_stream.py

+++ b/proj/hps_accel/gateware/stream/test_stream.py

@@ -13,14 +13,14 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Signal, Shape

-from nmigen.hdl.dsl import Module

-from nmigen.hdl.rec import Layout, Record

-from nmigen.sim.core import Delay

+from amaranth import Signal, Shape

+from amaranth.hdl.dsl import Module

+from amaranth.hdl.rec import Layout, Record

+from amaranth.sim.core import Delay

from .stream import Endpoint, connect

-from nmigen_cfu.util import SimpleElaboratable, TestBase

+from amaranth_cfu.util import SimpleElaboratable, TestBase

TEST_PAYLOAD_LAYOUT = Layout([

diff --git a/proj/mnv2_first/cfu_gen.py b/proj/mnv2_first/cfu_gen.py

index 8d8be4e57..9c9d51185 100644

--- a/proj/mnv2_first/cfu_gen.py

+++ b/proj/mnv2_first/cfu_gen.py

@@ -13,7 +13,7 @@

# limitations under the License.

import os.path

-from nmigen.back import verilog

+from amaranth.back import verilog

from gateware.mnv2_cfu import make_cfu

diff --git a/proj/mnv2_first/gateware/delay.py b/proj/mnv2_first/gateware/delay.py

index 8c698577d..7f813a11d 100644

--- a/proj/mnv2_first/gateware/delay.py

+++ b/proj/mnv2_first/gateware/delay.py

@@ -15,9 +15,9 @@

# Delayer temporarily moved out of the sequencing module to break a circular dependency

-from nmigen import Signal

+from amaranth import Signal

-from nmigen_cfu import SimpleElaboratable

+from amaranth_cfu import SimpleElaboratable

class Delayer(SimpleElaboratable):

diff --git a/proj/mnv2_first/gateware/macc.py b/proj/mnv2_first/gateware/macc.py

index 764dcb901..a4116d10a 100644

--- a/proj/mnv2_first/gateware/macc.py

+++ b/proj/mnv2_first/gateware/macc.py

@@ -13,9 +13,9 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Cat, Signal, signed

+from amaranth import Cat, Signal, signed

-from nmigen_cfu import all_words, SimpleElaboratable, tree_sum

+from amaranth_cfu import all_words, SimpleElaboratable, tree_sum

from .delay import Delayer

from .post_process import PostProcessor

diff --git a/proj/mnv2_first/gateware/mnv2_cfu.py b/proj/mnv2_first/gateware/mnv2_cfu.py

index da412fc9e..1287fdd57 100644

--- a/proj/mnv2_first/gateware/mnv2_cfu.py

+++ b/proj/mnv2_first/gateware/mnv2_cfu.py

@@ -13,9 +13,9 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Signal

-from nmigen.lib.fifo import SyncFIFOBuffered

-from nmigen_cfu import simple_cfu, DualPortMemory, is_pysim_run

+from amaranth import Signal

+from amaranth.lib.fifo import SyncFIFOBuffered

+from amaranth_cfu import simple_cfu, DualPortMemory, is_pysim_run

from . import config

from .macc import Accumulator, ByteToWordShifter, Madd4Pipeline

diff --git a/proj/mnv2_first/gateware/output.py b/proj/mnv2_first/gateware/output.py

index 1698eaca2..6222a0906 100644

--- a/proj/mnv2_first/gateware/output.py

+++ b/proj/mnv2_first/gateware/output.py

@@ -13,7 +13,7 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Signal

+from amaranth import Signal

from .registerfile import Xetter

class OutputQueueGetter(Xetter):

diff --git a/proj/mnv2_first/gateware/post_process.py b/proj/mnv2_first/gateware/post_process.py

index 80b8f8c14..37a2f62ee 100644

--- a/proj/mnv2_first/gateware/post_process.py

+++ b/proj/mnv2_first/gateware/post_process.py

@@ -13,9 +13,9 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Mux, Signal, signed

+from amaranth import Mux, Signal, signed

-from nmigen_cfu import SimpleElaboratable

+from amaranth_cfu import SimpleElaboratable

from .delay import Delayer

from .registerfile import Xetter

diff --git a/proj/mnv2_first/gateware/registerfile.py b/proj/mnv2_first/gateware/registerfile.py

index 54bedefd2..704e459d9 100644

--- a/proj/mnv2_first/gateware/registerfile.py

+++ b/proj/mnv2_first/gateware/registerfile.py

@@ -14,9 +14,9 @@

# limitations under the License.

-from nmigen import Signal

+from amaranth import Signal

-from nmigen_cfu import InstructionBase, SimpleElaboratable, ValueBuffer

+from amaranth_cfu import InstructionBase, SimpleElaboratable, ValueBuffer

class Xetter(SimpleElaboratable):

diff --git a/proj/mnv2_first/gateware/sequencing.py b/proj/mnv2_first/gateware/sequencing.py

index de320bc15..84bc9085a 100644

--- a/proj/mnv2_first/gateware/sequencing.py

+++ b/proj/mnv2_first/gateware/sequencing.py

@@ -13,9 +13,9 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Signal, Mux

+from amaranth import Signal, Mux

-from nmigen_cfu import SimpleElaboratable

+from amaranth_cfu import SimpleElaboratable

from . import config

from .delay import Delayer

diff --git a/proj/mnv2_first/gateware/store.py b/proj/mnv2_first/gateware/store.py

index 492893783..7d4fa09b8 100644

--- a/proj/mnv2_first/gateware/store.py

+++ b/proj/mnv2_first/gateware/store.py

@@ -13,9 +13,9 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Array, Signal, Mux, Cat

+from amaranth import Array, Signal, Mux, Cat

-from nmigen_cfu import SimpleElaboratable, is_pysim_run, DualPortMemory, SequentialMemoryReader

+from amaranth_cfu import SimpleElaboratable, is_pysim_run, DualPortMemory, SequentialMemoryReader

from .registerfile import Xetter

diff --git a/proj/mnv2_first/gateware/test_macc.py b/proj/mnv2_first/gateware/test_macc.py

index 55fee58ff..9855f0473 100644

--- a/proj/mnv2_first/gateware/test_macc.py

+++ b/proj/mnv2_first/gateware/test_macc.py

@@ -14,9 +14,9 @@

# limitations under the License.

-from nmigen.sim import Delay

+from amaranth.sim import Delay

-from nmigen_cfu import TestBase

+from amaranth_cfu import TestBase

from .macc import Accumulator, ByteToWordShifter

diff --git a/proj/mnv2_first/gateware/test_mnv2_cfu.py b/proj/mnv2_first/gateware/test_mnv2_cfu.py

index 35496e1a6..1fcc435d1 100644

--- a/proj/mnv2_first/gateware/test_mnv2_cfu.py

+++ b/proj/mnv2_first/gateware/test_mnv2_cfu.py

@@ -13,7 +13,7 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen_cfu import CfuTestBase, pack_vals

+from amaranth_cfu import CfuTestBase, pack_vals

from .mnv2_cfu import make_cfu

diff --git a/proj/mnv2_first/gateware/test_output.py b/proj/mnv2_first/gateware/test_output.py

index 566088298..eedd5e2f5 100644

--- a/proj/mnv2_first/gateware/test_output.py

+++ b/proj/mnv2_first/gateware/test_output.py

@@ -14,9 +14,9 @@

# limitations under the License.

-from nmigen.sim import Delay

+from amaranth.sim import Delay

-from nmigen_cfu import TestBase

+from amaranth_cfu import TestBase

from .output import OutputQueueGetter

diff --git a/proj/mnv2_first/gateware/test_post_process.py b/proj/mnv2_first/gateware/test_post_process.py

index 502cac70e..46f74225d 100644

--- a/proj/mnv2_first/gateware/test_post_process.py

+++ b/proj/mnv2_first/gateware/test_post_process.py

@@ -13,9 +13,9 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen.sim import Settle

+from amaranth.sim import Settle

-from nmigen_cfu import TestBase

+from amaranth_cfu import TestBase

from.post_process import PostProcessXetter, PostProcessor

diff --git a/proj/mnv2_first/gateware/test_registerfile.py b/proj/mnv2_first/gateware/test_registerfile.py

index fd92b48a2..e85d336b5 100644

--- a/proj/mnv2_first/gateware/test_registerfile.py

+++ b/proj/mnv2_first/gateware/test_registerfile.py

@@ -13,10 +13,10 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Signal

-from nmigen.sim import Settle

+from amaranth import Signal

+from amaranth.sim import Settle

-from nmigen_cfu import InstructionTestBase, TestBase

+from amaranth_cfu import InstructionTestBase, TestBase

from .registerfile import Xetter, RegisterSetter, RegisterFileInstruction

diff --git a/proj/mnv2_first/gateware/test_sequencing.py b/proj/mnv2_first/gateware/test_sequencing.py

index 7b761ee1c..9154bf879 100644

--- a/proj/mnv2_first/gateware/test_sequencing.py

+++ b/proj/mnv2_first/gateware/test_sequencing.py

@@ -14,9 +14,9 @@

# limitations under the License.

-from nmigen.sim import Delay

+from amaranth.sim import Delay

-from nmigen_cfu import TestBase

+from amaranth_cfu import TestBase

from .delay import Delayer

from .sequencing import Delayer, GateCalculator, Sequencer, UpCounter

diff --git a/proj/mnv2_first/gateware/test_store.py b/proj/mnv2_first/gateware/test_store.py

index 1b283f0ab..bfea47d5c 100644

--- a/proj/mnv2_first/gateware/test_store.py

+++ b/proj/mnv2_first/gateware/test_store.py

@@ -13,10 +13,10 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import Signal

-from nmigen.sim import Settle, Delay

+from amaranth import Signal

+from amaranth.sim import Settle, Delay

-from nmigen_cfu import InstructionTestBase, DualPortMemory, TestBase

+from amaranth_cfu import InstructionTestBase, DualPortMemory, TestBase

from .store import CircularIncrementer, InputStore, StoreSetter

from .registerfile import RegisterSetter, Xetter, RegisterFileInstruction

diff --git a/proj/proj_accel_1/cfu.py b/proj/proj_accel_1/cfu.py

index 4dbd70ff6..82e389e86 100644

--- a/proj/proj_accel_1/cfu.py

+++ b/proj/proj_accel_1/cfu.py

@@ -13,8 +13,8 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import *

-from nmigen_cfu import InstructionBase, TestBase, Cfu, CfuTestBase

+from amaranth import *

+from amaranth_cfu import InstructionBase, TestBase, Cfu, CfuTestBase

import unittest

diff --git a/proj/proj_accel_1/cfu_gen.py b/proj/proj_accel_1/cfu_gen.py

index 9864f0fee..7761d9841 100644

--- a/proj/proj_accel_1/cfu_gen.py

+++ b/proj/proj_accel_1/cfu_gen.py

@@ -13,8 +13,8 @@

# limitations under the License.

import os.path

-from nmigen import *

-from nmigen.back import rtlil, verilog

+from amaranth import *

+from amaranth.back import rtlil, verilog

from cfu import make_cfu

diff --git a/proj/proj_template/cfu.py b/proj/proj_template/cfu.py

index 0d7bdd367..3761c1231 100644

--- a/proj/proj_template/cfu.py

+++ b/proj/proj_template/cfu.py

@@ -13,8 +13,8 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import *

-from nmigen_cfu import InstructionBase, InstructionTestBase, simple_cfu, CfuTestBase

+from amaranth import *

+from amaranth_cfu import InstructionBase, InstructionTestBase, simple_cfu, CfuTestBase

import unittest

# See proj_example for further example instructions

diff --git a/proj/proj_template/cfu_gen.py b/proj/proj_template/cfu_gen.py

index 9864f0fee..7761d9841 100644

--- a/proj/proj_template/cfu_gen.py

+++ b/proj/proj_template/cfu_gen.py

@@ -13,8 +13,8 @@

# limitations under the License.

import os.path

-from nmigen import *

-from nmigen.back import rtlil, verilog

+from amaranth import *

+from amaranth.back import rtlil, verilog

from cfu import make_cfu

diff --git a/proj/tail_rom/cfu.py b/proj/tail_rom/cfu.py

index 22318e50e..3e5d34868 100644

--- a/proj/tail_rom/cfu.py

+++ b/proj/tail_rom/cfu.py

@@ -13,8 +13,8 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-from nmigen import *

-from nmigen_cfu import InstructionBase, InstructionTestBase, simple_cfu, CfuTestBase

+from amaranth import *

+from amaranth_cfu import InstructionBase, InstructionTestBase, simple_cfu, CfuTestBase

import unittest

# See proj_example for further example instructions

diff --git a/proj/tail_rom/cfu_gen.py b/proj/tail_rom/cfu_gen.py

index 9864f0fee..7761d9841 100644

--- a/proj/tail_rom/cfu_gen.py

+++ b/proj/tail_rom/cfu_gen.py

@@ -13,8 +13,8 @@

# limitations under the License.

import os.path

-from nmigen import *

-from nmigen.back import rtlil, verilog

+from amaranth import *

+from amaranth.back import rtlil, verilog

from cfu import make_cfu

diff --git a/python/nmigen_cfu/__init__.py b/python/amaranth_cfu/__init__.py

similarity index 95%

rename from python/nmigen_cfu/__init__.py

rename to python/amaranth_cfu/__init__.py

index c5cb2a112..9c858e111 100644

--- a/python/nmigen_cfu/__init__.py

+++ b/python/amaranth_cfu/__init__.py

@@ -14,6 +14,6 @@

# limitations under the License.

-__package__ = 'nmigen_cfu'

+__package__ = 'amaranth_cfu'

from .cfu import *

from .util import *

diff --git a/python/nmigen_cfu/cfu.py b/python/amaranth_cfu/cfu.py

similarity index 98%

rename from python/nmigen_cfu/cfu.py

rename to python/amaranth_cfu/cfu.py

index b4a7360ef..bd1c9cbf9 100644

--- a/python/nmigen_cfu/cfu.py

+++ b/python/amaranth_cfu/cfu.py

@@ -13,12 +13,12 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-__package__ = 'nmigen_cfu'

+__package__ = 'amaranth_cfu'

-from nmigen import Array, Signal, signed

-from nmigen.hdl.dsl import Module

+from amaranth import Array, Signal, signed

+from amaranth.hdl.dsl import Module

from .util import SimpleElaboratable, TestBase

-from nmigen.hdl import ResetSignal

+from amaranth.hdl import ResetSignal

class InstructionBase(SimpleElaboratable):

@@ -358,7 +358,7 @@ def simple_cfu(instructions):

"""Simplified API for CFUs.

This provides simplified API suitable for use only when each CFU

- instruction is independent of the others. This API breaks nmigen

+ instruction is independent of the others. This API breaks amaranth

conventions, and should only be used in very simple cases.

For more complex cases, subclass Cfu directly.

diff --git a/python/nmigen_cfu/run_unit_tests.sh b/python/amaranth_cfu/run_unit_tests.sh

similarity index 100%

rename from python/nmigen_cfu/run_unit_tests.sh

rename to python/amaranth_cfu/run_unit_tests.sh

diff --git a/python/nmigen_cfu/test_cfu.py b/python/amaranth_cfu/test_cfu.py

similarity index 99%

rename from python/nmigen_cfu/test_cfu.py

rename to python/amaranth_cfu/test_cfu.py

index 796802068..36f848d7e 100644

--- a/python/nmigen_cfu/test_cfu.py

+++ b/python/amaranth_cfu/test_cfu.py

@@ -16,11 +16,11 @@

#

# This file contains tests and examples

#

-__package__ = 'nmigen_cfu'

+__package__ = 'amaranth_cfu'

import math

-from nmigen import Signal

-from nmigen.sim import Delay

+from amaranth import Signal

+from amaranth.sim import Delay

from .cfu import simple_cfu, InstructionBase, InstructionTestBase

from .util import TestBase

diff --git a/python/nmigen_cfu/test_util.py b/python/amaranth_cfu/test_util.py

similarity index 97%

rename from python/nmigen_cfu/test_util.py

rename to python/amaranth_cfu/test_util.py

index 0bf726c3e..0697074a1 100644

--- a/python/nmigen_cfu/test_util.py

+++ b/python/amaranth_cfu/test_util.py

@@ -13,10 +13,10 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-__package__ = 'nmigen_cfu'

+__package__ = 'amaranth_cfu'

-from nmigen import Signal

-from nmigen.sim import Settle, Delay

+from amaranth import Signal

+from amaranth.sim import Settle, Delay

from .util import SequentialMemoryReader, TestBase, ValueBuffer, SequentialMemoryReader

diff --git a/python/nmigen_cfu/util.py b/python/amaranth_cfu/util.py

similarity index 96%

rename from python/nmigen_cfu/util.py

rename to python/amaranth_cfu/util.py

index 0571588c1..8e350d2c9 100644

--- a/python/nmigen_cfu/util.py

+++ b/python/amaranth_cfu/util.py

@@ -13,12 +13,12 @@

# See the License for the specific language governing permissions and

# limitations under the License.

-__package__ = 'nmigen_cfu'

+__package__ = 'amaranth_cfu'

-from nmigen import Elaboratable, Module, Mux, Signal, Memory

-from nmigen.build import Platform

-from nmigen.hdl.ast import Cat

-from nmigen.sim import Simulator

+from amaranth import Elaboratable, Module, Mux, Signal, Memory

+from amaranth.build import Platform

+from amaranth.hdl.ast import Cat

+from amaranth.sim import Simulator

import unittest

@@ -96,7 +96,7 @@ def elaborate(self, platform: Platform):

class _DummySyncModule(SimpleElaboratable):

"""A module that does something arbirarty with synchronous logic

- This is used by TestBase to stop nMigen from complaining if our DUT doesn't

+ This is used by TestBase to stop Amaranth from complaining if our DUT doesn't

contain any synchronous logic."""

def elab(self, m):

@@ -105,7 +105,7 @@ def elab(self, m):

class TestBase(unittest.TestCase):

- """Base class for testing an nMigen module.

+ """Base class for testing an Amaranth module.

The module can use sync, comb or both.

"""

diff --git a/scripts/setup b/scripts/setup

index 355bcd025..950174859 100755

--- a/scripts/setup

+++ b/scripts/setup

@@ -1,5 +1,12 @@

#!/bin/bash

set -e

+

+# Clean up obsolete nmigen directory, if present

+if [ -d third_party/python/nmigen ] ; then

+ rm -rf third_party/python/nmigen

+fi

+

+# Bring in submodules